# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10)授权公告号 CN 103795060 B (45)授权公告日 2015.11.18

(21)申请号 201410066430.3

(22)申请日 2014.02.26

(73) **专利权人** 中南大学 **地址** 410083 湖南省长沙市岳麓区麓山南路 932 号

(72) **发明人** 于晶荣 徐勇 陈岗 邹勇军 程美红

(74) **专利代理机构** 长沙市融智专利事务所 43114

代理人 黄美成

(51) Int. CI.

*H02J 3/01*(2006.01)

#### (56) 对比文件

CN 102468651 A, 2012. 05. 23, 说明书 0002-0055 段, 附图 1-5.

CN 102857133 A, 2013.01.02, 全文.

CN 103414327 A, 2013. 11. 27, 说明书

0002-0023 段,附图 1-4.

CN 201234137 Y, 2009.05.06, 全文. US 2010134204 A1, 2010.06.03, 全文.

审查员 于淼

权利要求书3页 说明书13页 附图3页

## (54) 发明名称

有源电力滤波器的输出滤波电路、滤波方法 及设计方法

#### (57) 摘要

本发明公开了一种有源电力滤波器的输出滤波电路、滤波方法及设计方法,有源电力滤波器的输出滤波电路由逆变器侧电感  $L_1$ 、网侧电感  $L_2$ 、网侧并联电阻  $R_g$ 、阻尼支路  $R_d$ C<sub>d</sub>、高通支路  $C_h$ 、单倍开关谐波支路  $C_f$ L<sub>f</sub>、双倍开关谐波支路  $C_f$ L<sub>f</sub>组成。本发明的 DRLCL 电路可以有效的滤除 1kHz 以上的高次谐波,单倍及双倍开关谐波,滤波效果完全满足 1EEE519-1992 关于各次谐波的要求,并且不会增加控制系统的复杂性。

1. 一种有源电力滤波器的输出滤波电路,其特征在于,由逆变器侧电感  $L_1$ 、网侧电感  $L_2$ 、网侧并联电阻  $R_g$ 、阻尼支路、高通支路  $C_h$ 、单倍开关谐波支路、双倍开关谐波支路构成;

记网侧的正端为 A、并联支路公共点为 B、逆变侧的正输出端为 C、逆变侧的负输出端和 网侧的负端短接点为 D:

逆变器侧电感  $L_1$ 接在 B 和 C 之间; 网侧电感  $L_2$ 和网侧并联电阻  $R_g$ 并联的 A 和 B 之间; 阻尼支路、高通支路  $C_h$ 、单倍开关谐波支路和双倍开关谐波支路均并联在 B 和 D 之间;

所述的阻尼支路由电阻 R<sub>d</sub>和电容 C<sub>d</sub>串接而成;

所述的单倍开关谐波支路由电容 C<sub>r</sub>和电感 L<sub>f</sub>串接而成;

所述的双倍开关谐波支路由电容 Cga和电感 Lga串接而成;

(1) 逆变器侧电感 L<sub>1</sub>满足下式:

$$\frac{U_{dc}T_s}{8\times10\%I_{refin}} < L_1 < \frac{5U_{dc}T_s}{3\Delta i_{ref}}$$

其中, $I_{refm}$ 是有源电力滤波器输出峰值电流, $U_{dc}$ 是直流电压,Ts 是开关周期, $\triangle$   $i_{ref}$ 为一个控制周期参考电流变化量,取为有源电力滤波器的输出电流的 1/5;

(2) 所述的网侧电感 L<sub>2</sub>与并联电容总和 C<sub>211</sub>设计满足:

网侧电感  $L_2$ 和并联的总电容是抑制并网输出电流高频纹波,对低频段影响很小,所以两个参数的设计要综合考虑;电感  $L_1+L_2$ 上的总压降不能高于逆变器接入电网点总电压的 10%,同时为了保证有源电力滤波器的低频控制性能和高频滤波性能, LCL 输出滤波电路的谐振频率  $f_{res}$ 设计为: $10f_1$ < $f_{res}$ <0.  $5f_s$ ,  $f_1$ 是基波频率,  $f_s$ 是单倍开关频率;

$$f_{res} = \frac{1}{2\pi} \sqrt{\frac{L_1 + L_2}{L_1 L_2 C_{all}}}$$

, 并联电容的总数值要满足装置的无功功率的要求:并联支路总电容的

无功容量要求小于装置无功容量的 5%; $C_{all}$ 为所有并联支路电容的代数和, $C_{all}$ 的表达式为  $C_{all} = C_h + C_f + C_f + C_d$ ;

(3) 并联支路其余参数设计满足:

$$\begin{cases} C_d = \frac{1}{2}C_{all} \\ C_h = \frac{1-k}{2}C_{all} \\ C_f = \frac{20k}{54}C_{all}, C_{fd} = \frac{7k}{54}C_{all} \end{cases}$$

,其中 k 为滤波配比因子,根据系统谐振峰值最低

点来确定; $C_{all}$ 为所有并联支路电容的代数和, $C_{all}$ 的表达式为 $C_{all} = C_h + C_f + C_{fd} + C_d$ ;

(4) R<sub>d</sub>的选取:

选取  $1\Omega \langle R_d \langle 3\Omega;$

网侧并联电阻 R。的设计

先根据下面表达式确定并联谐振频率 fsp,再根据关系图的沟壑带选取 Rg 的取值;

$$f_{sp} = \frac{1}{2\pi} \sqrt{\frac{C_f + C_{fd}}{C_f C_{fd} (L_{fd} + L_f)}} \;;$$

所述的关系图是下式中分母模值  $|R_{o}Z_{fm}+Z_{fe}|$  与频率 f 和  $R_{o}$ 的关系图;

$$Z_{//R} = \frac{R_{g} Z_{fz}}{R_{g} Z_{fm} + Z_{fz}}$$

其中, Z/R为 R。与两条并联的开关谐波支路的并联阻抗;

$$Z_{fz} = s^4 L_f C_f L_{fd} C_{fd} + s^2 (L_f C_f + L_{fd} C_{fd}) + 1$$

$Z_{fm} = s^3 C_f C_{fd} (L_f + L_{fd}) + s (C_f + C_{fd})$  , s 表示频域的因子,即 s = j  $\omega$  。

- 2. 一种有源电力滤波器的输出滤波方法,其特征在于,采用权利要求1所述的有源电 力滤波器的输出滤波电路滤除 1kHz 以上的高次谐波,单倍及双倍开关谐波。

- 3. 一种有源电力滤波器的输出滤波电路的设计方法, 其特征在于, 所述的输出滤波电 路为权利要求1所述的有源电力滤波器的输出滤波电路:各参数的确定过程如下:

- (1) 逆变器侧电感 L,满足下式:

$$\frac{U_{dc}T_s}{8\times10\%I_{refin}} < L_1 < \frac{5U_{dc}T_s}{3\Delta i_{ref}}$$

其中,I<sub>refm</sub>是有源电力滤波器输出峰值电流,U<sub>dc</sub>是直流电压,Ts 是开关周期,△ i<sub>ref</sub>为 一个控制周期参考电流变化量,取为有源电力滤波器的输出电流的 1/5;

(2) 所述的网侧电感 Lo与并联电容总和 Call设计满足:

网侧电感 L。和并联的总电容是抑制并网输出电流高频纹波,对低频段影响很小, 所以两个参数的设计要综合考虑;电感 L<sub>1</sub>+L<sub>2</sub>上的总压降不能高于逆变器接入电网点总 电压的 10%,同时为了保证有源电力滤波器的低频控制性能和高频滤波性能,LCL 输出 滤波电路的谐振频率  $f_{res}$ 设计为:  $10f_1 < f_{res} < 0.5f_s$ ,  $f_1$ 是基波频率,  $f_s$ 是单倍开关频率;

$$f_{res} = \frac{1}{2\pi} \sqrt{\frac{L_1 + L_2}{L_1 L_2 C_{ell}}}$$

,并联电容的总数值要满足装置的无功功率的要求:并联支路总电容的

无功容量要求小于装置无功容量的5%;Call为所有并联支路电容的代数和,Call的表达式为  $C_{a11} = C_{b} + C_{f} + C_{fd} + C_{d};$

(3) 并联支路其余参数设计满足:

$$\begin{cases} C_d = \frac{1}{2}C_{all} \\ C_h = \frac{1-k}{2}C_{all} \\ C_f = \frac{20k}{54}C_{all}, C_{fd} = \frac{7k}{54}C_{all} \end{cases}$$

,其中 k 为滤波配比因子,根据系统谐振峰值最低 确定: $C_{all}$ 为所有并联支路电容的代数和, $C_{all}$ 的表达式为  $C_{all} = C_b + C_a + C_{ad} + C_d$ :

点来确定; $C_{all}$ 为所有并联支路电容的代数和, $C_{all}$ 的表达式为 $C_{all} = C_b + C_f + C_{fd} + C_d$ ;

(4) R<sub>d</sub>的选取:

选取  $1\Omega \langle R_d \langle 3\Omega ;$

网侧并联电阻 R。的设计

先根据下面表达式确定并联谐振频率 fsp,再根据关系图的沟壑带选取 Rg 的取值;

$$f_{sp} = \frac{1}{2\pi} \sqrt{\frac{C_f + C_{fd}}{C_f C_{fd} (L_{fd} + L_f)}} \; ;$$

所述的关系图是下式中分母模值  $|R_{g}Z_{fm}+Z_{fz}|$  与频率 f 和  $R_{g}$ 的关系图;

$$Z_{//R} = \frac{R_{g} Z_{fz}}{R_{g} Z_{fm} + Z_{fz}}$$

其中, $Z_{I/R}$ 为  $R_g$ 与两条并联的开关谐波支路的并联阻抗;

$$Z_{fz} = s^4 L_f C_f L_{fd} C_{fd} + s^2 (L_f C_f + L_{fd} C_{fd}) + 1$$

$Z_{fm} = s^3 C_f C_{fd} (L_f + L_{fd}) + s (C_f + C_{fd})$  , s 表示频域的因子,即 s = j  $\omega$  。

# 有源电力滤波器的输出滤波电路、滤波方法及设计方法

#### 技术领域

[0001] 本发明涉及一种有源电力滤波器的输出滤波电路、滤波方法及设计方法,属于电力电子装置设计领域。

## 背景技术

[0002] 随着现代工业的发展,电力电子变流装置的使用越来越广泛,电力电子的应用程度已成为了工业现代化的重要标志。同时,由于电网中大量电力电子设备的应用,电压和电流的波形都产生了严重的畸变,因为电力电子器件都带有非线性因素,一方面它能够满足人们对电能日益增长的各种需求,另一方面,大量的电力电子元件的使用会对电网供电质量造成谐波污染,谐波引起的各种事故也不断发生。现代企业及一些敏感设备对电能质量的要求比较高,谐波污染已成为电力系统的公害之一,受到了人们的广泛关注。

[0003] 随着电力电子技术的发展,谐波抑制技术也取得了突破性的进展,主要包括主动谐波治理(多重或者多电平逆变技术;软开关技术;PWM整流技术)和被动谐波治理(无源滤波和有源滤波)。无源滤波技术因为结构简单,成本低廉,技术难度低被广泛应用,但是其谐波治理效果差,难以达到滤波要求,并且极易发生谐振。而有源电力滤波器不但能弥补无源滤波器的不足,同时还能准确、动态的补偿谐波电流,滤波效果很好。

[0004] 但是有源电力滤波器采用 PWM 调制技术,输出电流中含有丰富的高频谐波和开关谐波,传统的 L和 LCL 输出滤波电路难以在保证有源电力滤波器带宽的同时,有效抑制高次开关谐波,不能满足 IEEE519-1992 关于谐波的要求。为兼顾有源电力滤波器系统带宽和高次谐波抑制两方面性能要求,有必要设计一种有源电力滤波器的输出滤波电路、滤波方法及设计方法。

## 发明内容

[0005] 本发明所要解决的技术问题是提供一种有源电力滤波器的输出滤波电路、滤波方法及设计方法,该有源电力滤波器的输出滤波电路及滤波方法易于实施,且滤波效果好。

[0006] 发明的技术解决方案如下:

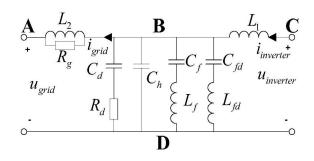

[0007] 一种有源电力滤波器的输出滤波电路,由逆变器侧电感  $L_1$ 、网侧电感  $L_2$ 、网侧并联电阻  $R_a$ 、阻尼支路、高通支路  $C_b$ 、单倍开关谐波支路、双倍开关谐波支路构成;

[0008] 记网侧的正端为 A、并联支路公共点为 B、逆变侧的正输出端为 C、逆变侧的负输出端和网侧的负端短接点为 D;

[0009] 逆变器侧电感  $L_1$ 接在 B 和 C 之间; 网侧电感  $L_2$ 和网侧并联电阻  $R_g$ 并联的 A 和 B 之间; 阻尼支路、高通支路  $C_h$ 、单倍开关谐波支路和双倍开关谐波支路均并联在 B 和 D 之间;

[0010] 所述的阻尼支路由 R<sub>a</sub>和 C<sub>a</sub>串接而成;

[0011] 所述的单倍开关谐波支路由 C<sub>f</sub>和 L<sub>f</sub>串接而成;

[0012] 所述的双倍开关谐波支路由 C<sub>fd</sub>和 L <sub>fd</sub>串接而成。

[0013] (1) 逆变器侧电感 L<sub>1</sub>满足下式:

$$[0014] \qquad \frac{U_{dc}T_{s}}{8\times10\%I_{refin}} < L_{1} < \frac{5U_{dc}T_{s}}{3\Delta i_{ref}}$$

[0015] 其中, $I_{refm}$ 是有源电力滤波器输出峰值电流, $U_{dc}$ 是直流电压,Ts 是开关周期, $\triangle i_{ref}$ 为一个控制周期参考电流变化量,取为有源电力滤波器的输出电流的 1/5;

[0016] (2) 所述的网侧电感 L<sub>2</sub>与并联电容总和 C<sub>311</sub>设计满足:

[0017] 网侧电感  $L_2$ 和并联的总电容是抑制并网输出电流高频纹波,对低频段影响很小,所以两个参数的设计要综合考虑。电感  $L_1+L_2$ 上的总压降不能高于逆变器接入电网点总电压的 10%,同时为了保证有源电力滤波器的低频控制性能和高频滤波性能,LCL 输出滤波电路的谐振频率  $f_{res}$ 设计为  $:10f_1 < f_{res} < 0.5f_s$ ,  $f_1$ 是基波频率,  $f_s$ 是单倍开关频率;

$$f_{res} = \frac{1}{2\pi} \sqrt{\frac{L_1 + L_2}{L_1 L_2 C_{all}}}$$

, 并联电容的总数值要满足装置的无功功率的要求:并联支路总电容的

无功容量要求小于装置无功容量的 5%;  $C_{a11}$ 的表达式为  $C_{a11}$ = $C_h$ + $C_f$ + $C_{fd}$ + $C_d$ 【DRLCL 滤波电路整体上的低通滤波特性及转折频率应与传统 LCL 滤波电路一致, 所以  $C_{a11}$ 的值对应传统 LCL 滤波电路的电容, 同时为所有并联支路电容的代数和。】

[0018] 【一股无功功率计算是仅考虑基波的,所以这里直接采用工频计算。】

[0019] (3) 并联支路其余参数设计满足:

$$\begin{bmatrix} C_d = \frac{1}{2} C_{all} \\ C_h = \frac{1-k}{2} C_{all} \\ C_f = \frac{20k}{54} C_{all}, C_{fd} = \frac{7k}{54} C_{all} \end{bmatrix}, 其中 k 为滤波配比因子,根据系统谐振峰值$$

最低点来确定:【所以k值匹配相应的DRLCL参数;

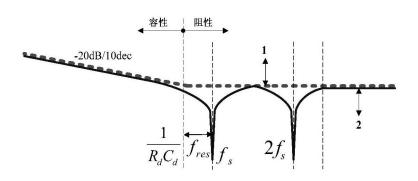

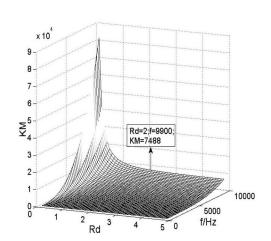

[0021] 具体 k 值选取方法为:绘制  $R_d = 0$  时,滤波系数  $K_M$ 和 k,谐振频率 f 的三维关系图;这个图根据后面的  $K_M$ 表达式得到。

[0023] 【所述的单倍开关谐波支路和双倍开关谐波支路的阻抗包括一个并联谐振点和两个串联谐振点,对应的频率解分别为:

[0024]

$$f_s = \frac{1}{2\pi\sqrt{L_f C_f}}, 2f_s = \frac{1}{2\pi\sqrt{L_{fd} C_{fd}}}$$

$$f_{sp} = \frac{1}{2\pi}\sqrt{\frac{C_f + C_{fd}}{C_f C_{fd} (L_{fd} + L_f)}}$$

[0025] 为保证两个谐振支路的滤波 Q 值相等,上述解还应满足:

[0026]

$$2f_s - f_{sp} = f_{sp} - f_s = \frac{1}{2}f_s$$

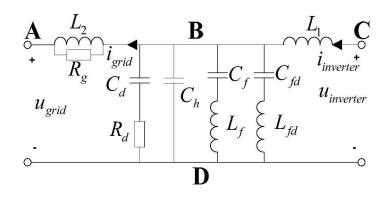

[0027] 当  $C_h + C_f + C_{fd} = C'$ ,所述的并联支路中的去除高通支路  $C_h$ 的其他部分在低频段与 C'和电阻 R'构成的串联阻尼支路阻抗特性一致,区别仅在两个开关谐振点,如附图 2。所以并联支路简化为 R' C' 阻尼支路和高通支路  $C_h$ 并联。为均衡阻尼损耗和高频衰减效果, $C_h$ 设计与 C' 相等,即满足:

$$\begin{bmatrix} C_h + C_f + C_{fd} = C_d = \frac{1}{2}C_{all} \\ C_h = \frac{1-k}{2}C_{all} \\ C_f = \frac{20k}{54}C_{all}, C_{fd} = \frac{7k}{54}C_{all} \end{bmatrix}$$

[0029] 所述的滤波系数  $K_M$ 对应系统谐振频率取最小值时,参照附图 3:3 : 当频率取得系统的谐振频率时,寻找  $K_M$ 的最小值即可确定最优 k=0.37 ;附图 3 表示阻尼电阻 Rd 为 0 时候的关系图,此时没有阻尼作用,对应不同的 k 值,谐振频率 f=5.7 kHz 都有不同的谐振峰值,要想系统稳定,峰值应该选取最小,所以可以选取 k=0.37 最为合适。】

[0030] (4) R<sub>d</sub>的选取:

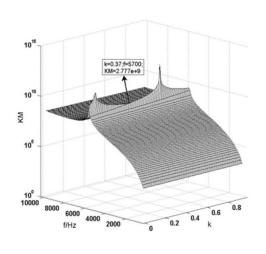

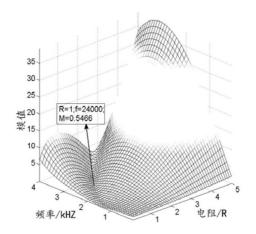

[0031] 选取  $1\Omega < R_d < 3\Omega$ ;【应考虑阻尼损耗和高频谐波的滤波效果,一定范围内,其数值增大,滤波效果会变好,但是损耗会增加,数值减小,滤波效果会变差。参照附图 4,: $R_d > 1$  时,5kHz-10kHz 频段的滤波系数基本不变,结合  $R_d$ 的选取原则确定  $R_d$ 的值,本发明选取为  $2\Omega$ 。结合附图 4 和阻尼损耗尽量小的原则,所以  $1 < R_d < 3\Omega$  较为合适。】

[0032] (1) 网侧并联电阻 R。的设计

[0033] 先根据下面表达式确定并联谐振频率 fsp,再根据关系图的沟壑带选取 Rg 的取值:

[0034]

$$f_{sp} = \frac{1}{2\pi} \sqrt{\frac{C_f + C_{fd}}{C_f C_{fd} (L_{fd} + L_f)}} ;$$

[0035] 所述的关系图是下式中分母模值  $|R_gZ_{fm}+Z_{fz}|$  与频率 f 和  $R_g$ 的关系图;

[0036]

$$Z_{//R} = \frac{R_g Z_{fz}}{R_g Z_{fm} + Z_{fz}}$$

[0037] 【说明:这个图绘制用不到 fsp,图 z 轴为分母模值  $|R_gZ_{fm}+Z_{fz}|$ ,y 轴为  $R_g$ ,x 轴为频率 f(f= $\omega$  / 2 $\pi$ )(这个  $\omega$  是下式中 s 包含的那个  $\omega$ ,均为角频率,是变量),三个变量,用 matlab 即可绘制出相应关系。】

[0038] 其中,

[0039]  $Z_{fz} = s^4 L_f C_f L_{fd} C_{fd} + s^2 (L_f C_f + L_{fd} C_{fd}) + 1$

[0040]  $Z_{fm}=s^3C_fC_{fd}(L_f+L_{fd})+s(C_f+C_{fd})$ , s 表示频域的因子,即  $s=j\omega$ 。

[0041] 【所述的网侧并联电阻  $R_g$ 并联在网侧电感  $L_2$ 两侧,由于网侧电压并不产生谐波,所以对于谐波而言网侧相当于短路,即电阻与两条并联的开关谐波支路相当于,主要用与抑制两条并联的开关谐波支路的并联谐振点,同时配合  $R_d$ 抑制整个 DRLCL 电路系统的谐振点,由于网侧电感  $L_2$ 的内阻非常小,所有的输出电流几乎从网侧电感  $L_2$ 上流过,而  $R_g$ 上几

乎没有电流,所以  $R_g$ 损耗非常小,这样电阻  $R_g$ 不但能承担电阻  $R_d$ 的部分作用,还有利于减少系统的总损耗,同时还能抑制两条并联的开关谐波支路的并联谐振点。 $R_g$ 与两条并联的开关谐波支路的并联阻抗  $Z_{//R}$ 为:

[0042]

$$Z_{//R} = \frac{R_g Z_{fz}}{R_g Z_{fm} + Z_{fz}}$$

[0043] 其中,

[0044]  $Z_{fz} = S^4 L_f C_f L_{fd} C_{fd} + S^2 (L_f C_f + L_{fd} C_{fd}) + 1$

[0045]  $Z_{fm}=s^3C_fC_{fd}(L_f+L_{fd})+s(C_f+C_{fd})$ , s表示频域的因子,即  $s=j\omega$ :

[0046] 根据所述的  $Z_{//R}$  表达式绘制出分母模值  $|R_g Z_{fm} + Z_{fz}|$  与频率 f 和  $R_g$ 的关系图(附图 5),  $R_g$ 的选取应遵循: $Z_{//R}$ 的分母模值在并联谐振频率处取最小值,结合这个原则并参考附图 5 中的沟壑带选取  $R_g$ 的数值,从附图 5 中可以看到对应不同的并联谐振频率,都有一组  $R_g$ 值满足沟壑带。图 5 反映的  $Z_{//R}$ 的固有特性,即谐振频率处对应的  $Z_{//R}$ 的分母模值为最小。】

[0047] 一种有源电力滤波器的输出滤波方法,采用前述的有源电力滤波器的输出滤波电路滤除 1kHz 以上的高次谐波,单倍及双倍开关谐波。

[0048] 一种有源电力滤波器的输出滤波电路的设计方法,所述的输出滤波电路为前述的有源电力滤波器的输出滤波电路;各参数的确定过程如下:

[0049] (1) 逆变器侧电感 Li满足下式:

$$[0050] \qquad \frac{U_{dc}T_{s}}{8\times10\%I_{refim}} < L_{1} < \frac{5U_{dc}T_{s}}{3\Delta i_{ref}}$$

[0051] 其中, $I_{refm}$ 是有源电力滤波器输出峰值电流, $U_{dc}$ 是直流电压,Ts 是开关周期, $\triangle i_{ref}$ 为一个控制周期参考电流变化量,取为有源电力滤波器的输出电流的 1/5;

[0052] (2) 所述的网侧电感 L<sub>2</sub>与并联电容总和 C<sub>all</sub>设计满足:

[0053] 网侧电感  $L_2$ 和并联的总电容是抑制并网输出电流高频纹波,对低频段影响很小,所以两个参数的设计要综合考虑。电感  $L_1+L_2$ 上的总压降不能高于逆变器接入电网点总电压的 10%,同时为了保证有源电力滤波器的低频控制性能和高频滤波性能,LCL 输出滤波电路的谐振频率  $f_{res}$ 设计为:

[0054]

$$10f_1 < f_{res} < 0.5f_s$$

, $f_1$ 是基波频率, $f_s$ 是单倍开关频率; $f_{res} = \frac{1}{2\pi} \sqrt{\frac{L_1 + L_2}{L_1 L_2 C_{all}}}$ ,并联电

容的总数值要满足装置的无功功率的要求:并联支路总电容的无功容量要求小于装置无功容量的 5%; $C_{all}$ 的表达式为  $C_{all}$ = $C_h$ + $C_f$ + $C_d$ ;

[0055] (3) 并联支路其余参数设计满足:

$$\begin{bmatrix} C_d = \frac{1}{2} C_{all} \\ C_h = \frac{1-k}{2} C_{all} \\ C_f = \frac{20k}{54} C_{all}, C_{fd} = \frac{7k}{54} C_{all} \end{bmatrix}, 其中 k 为滤波配比因子,根据系统谐$$

[0057] 振峰值最低点来确定;

[0058] (4) R<sub>d</sub>的选取:

[0059] 选取  $1\Omega \langle R_d \langle 3\Omega ;$

[0060] 网侧并联电阻 R。的设计

[0062]

$$f_{sp} = \frac{1}{2\pi} \sqrt{\frac{C_f + C_{fd}}{C_f C_{fd} (L_{fd} + L_f)}} ;$$

[0063] 所述的关系图是下式中分母模值  $|R_gZ_{fm}+Z_{fz}|$  与频率 f 和  $R_g$ 的关系图;

[0064]

$$Z_{//R} = \frac{R_g Z_{fz}}{R_g Z_{fm} + Z_{fz}}$$

[0065] 其中,

[0066]  $Z_{fz} = s^4 L_f C_f L_{fd} C_{fd} + s^2 (L_f C_f + L_{fd} C_{fd}) + 1$

[0067]  $Z_{fm}=s^3C_fC_{fd}(L_f+L_{fd})+s(C_f+C_{fd})$ , s 表示频域的因子,即  $s=j\omega$ .

[0068] 该输出滤波电路在传统的 LCL 输出滤波电路的基础上增加了 RC 阻尼支路和两条 LC 谐振支路,同时在网侧小电感上并联电阻,设计过程清晰,所述的 DRLCL 滤波电路可以有效滤除高频谐波,及单双倍开关谐波。

[0069] 所述的逆变器侧电感  $L_1$ 用于平滑电压纹波; 网侧电感  $L_2$ 用于抑制高频谐波; 阻尼支路  $R_dC_d$ 用来抑制 LCL 电路结构的并联谐振尖峰, 本电路谐振频率设计在 6kHz; 两条 LC 开关谐振支路分别在  $f_s$ (单倍开关频率)和  $2f_s$ 处谐振, 即在这两处频率为零阻抗; 由于阻尼电阻  $R_d$ 的存在, 高频衰减速度会减小,所以通过单电容支路  $C_h$ 是改善高频衰减特性; 由于有两个并联开关谐振支路,所以会在  $f_s$ 和  $2f_s$ 之间引入一个并联谐振点,即本发明所述的  $f_{sp}$ ,会导致系统不稳定,用网侧并联  $R_g$ 来抑制这个并联谐振影响。

[0070] 所述的 DRLCL 电路设计方法为:

[0071] DRLCL 电路设计顺序上先要设计逆变器侧电感  $L_1$ 的取值,然后确定网侧电感  $L_2$ 的值,进而根据相对应的 LCL 滤波要求设计总电容取值,最后讨论并联支路每个参数的设计方法。

[0072] 逆变器侧电感  $L_1$ 与网侧电感  $L_2$ 与并联电容总和  $C_{all}$ 选取原则与普通的 LCL 参数设计一样。

[0073]  $L_1$ 上同时流过了装置输出的低频谐波电流和开关纹波电流,所以  $L_1$ 的设计既要满足电流跟踪能力的要求,又要满足满足开关纹波电流的要求。即要满足表达式:

$$[0074] \qquad \frac{U_{dc}T_{s}}{8\times10\%I_{refin}} < L_{1} < \frac{5U_{dc}T_{s}}{3\Delta i_{ref}}$$

[0075] 其中, $I_{refm}$ 是有源电力滤波器输出峰值电流, $U_{dc}$ 是直流电压(700V),Ts 是开关周期(1/16000s), $\triangle i_{ref}$ 为一个控制周期参考电流变化量,可以取为有源电力滤波器输出电流的 1/5。

[0076] DRLCL 的电容设计要参考基本 LCL 参数设计,网侧电感  $L_2$ 和并联的总电容是抑制并网输出电流高频纹波,对低频段影响很小,所以两个参数的设计要综合考虑。电感  $L_1+L_2$  上的总压降不能高于 10%,同时为了保证有源电力滤波器的低频控制性能和高频滤波性能,LCL 输出滤波电路的谐振频率  $f_{res}$ 一股设计为  $:10f_1 < f_{res} < 0.5f_s$ ,  $f_1$ 是基波频率,  $f_s$ 是单倍开关频率。并联电容的总数值要满足装置的无功功率的要求 : 并联支路总电容的无功容量要求小于装置无功容量的 5%。谐振频率表达式为 :

[0077]

$$f_{res} = \frac{1}{2\pi} \sqrt{\frac{L_1 + L_2}{L_1 L_2 C_{all}}}$$

[0078] 所述的 DRLCL 电路中 R<sub>g</sub>的主要作用是抑制两条谐振支路并联谐振峰值的作用,对于所需要的滤波频段的滤波性能几乎没有影响,所以对并联支路参数的影响可以忽略,讨论并联支路参数设计时, R<sub>g</sub>阻抗不计入在内。

[0079] 所述的单倍开关谐波支路和双倍开关谐波支路的阻抗包括一个并联谐振点和两个串联谐振点,对应的频率解分别为:

[0080]

$$f_s = \frac{1}{2\pi\sqrt{L_f C_f}}, 2f_s = \frac{1}{2\pi\sqrt{L_{fd} C_{fd}}}$$

[0081]

$$f_{sp} = \frac{1}{2\pi} \sqrt{\frac{C_f + C_{fd}}{C_f C_{fd} (L_{fd} + L_f)}}$$

[0082] 为保证两个谐振支路的滤波 Q 值相等,上述解还应满足:

[0083]

$$2f_s - f_{sp} = f_{sp} - f_s = \frac{1}{2}f_s$$

[0084] 当  $C_h+C_f+C_{fd}=C'$ ,所述的并联支路中的去除高通支路  $C_h$ 的其他部分在低频段与 C'和电阻 R'构成的单一串联阻尼支路阻抗特性一致,区别仅在单倍及双倍开关谐振频率。所以所述的并联支路可以简化为 R' C' 阻尼支路和高通支路  $C_h$  并联。为均衡阻尼损耗和高频衰减效果, $C_h$ 设计与 C' 相等,即满足:

$$\begin{cases} C_{h} + C_{f} + C_{fd} = C_{d} = \frac{1}{2}C_{all} \\ C_{h} = \frac{1-k}{2}C_{all} \\ C_{f} = \frac{20k}{54}C_{all}, C_{fd} = \frac{7k}{54}C_{all} \end{cases}$$

[0086] 其中 0<k<1。

[0087] 由于电网电压不产生谐波,所以就谐波而言,电网侧相当于短路,所述的 DRLCL 滤波系数为 K<sub>u</sub>为逆变侧流经电感 L<sub>1</sub>的电流与网侧剩余电流之比的模:

[0088]

$$K_{M} = \left| \frac{i_{grid}(s)}{i_{invertor}(s)} \right| = \left| \frac{x + yj}{x_{1} + y_{1}j} \right|$$

[0089] 其中,

$$\begin{cases} x = \left(\frac{\omega^{2}}{\omega_{s1}^{2}} - 1\right) \left(\frac{\omega^{2}}{\omega_{s2}^{2}} - 1\right) \\ y = \frac{\omega R_{d} C_{all}}{2} \left(\frac{\omega^{2}}{\omega_{s1}^{2}} - 1\right) \left(\frac{\omega^{2}}{\omega_{s2}^{2}} - 1\right) \\ x_{1} = 1 - \omega^{2} \left(L_{2} C_{all} + \frac{1}{\omega_{s1}^{2}} + \frac{1}{\omega_{s2}^{2}}\right) + \omega^{4} \left[\frac{L_{2} C_{all}}{\omega_{s1}^{2}} \left(1 - \frac{20}{54}k\right) + \frac{L_{2} C_{all}}{\omega_{s2}^{2}} \left(1 - \frac{7}{54}k\right) + \frac{1}{\omega_{s1}^{2} \omega_{s2}^{2}} \right] \\ -\omega^{6} \frac{(2 - k)L_{2} C_{all}}{2\omega_{s1}^{2} \omega_{s2}^{2}} \\ y_{1} = \frac{\omega R_{d} C_{all}}{2} - \omega^{3} R_{d} \left[\frac{L_{2} C_{all}^{2}}{4} + \frac{C_{all}}{2} \left(\frac{1}{\omega_{s1}^{2}} + \frac{1}{\omega_{s2}^{2}}\right)\right] \\ +\omega^{5} R_{d} \left[\frac{L_{2} C_{all}^{2}}{4\omega_{s1}^{2}} \left(1 - \frac{20}{27}k\right) + \frac{L_{2} C_{all}^{2}}{4\omega_{s2}^{2}} \left(1 - \frac{7}{27}k\right) + \frac{C_{all}}{2\omega_{s1}^{2} \omega_{s2}^{2}}\right] - \omega^{7} \frac{L_{2} R_{d} (1 - k) C_{all}^{2}}{4\omega_{s1}^{2} \omega_{s2}^{2}} \end{cases}$$

[0092]  $\omega$  是系统的各次谐波的角频率, $\omega_{s1}$ 是单倍开关谐波角频率, $\omega_{s2}$ 是双倍开关谐波角频率, $C_{a11}$ 是所述并联支路的所有电容的代数和。当  $R_d$ =0 时,通过绘制出  $K_M$ 和 k,f 的三维关系图(附图 3),k 的最优值应满足滤波系数对应系统谐振频率取最小值,参照附图 3: 当频率取得系统的谐振频率时,寻找  $K_M$ 的最小值即可确定最优 k 值。

[0093] 选取最佳 k 值以后,通过绘制  $K_M$ 和  $R_d$ , f 的的关系确定  $R_d$ ,  $R_d$ 的选取原则:应考虑阻尼损耗和高频谐波的滤波效果,一定范围内,其数值增大,滤波效果会变好,但是损耗会增加,数值减小,滤波效果会变差。参照附图 4,: $R_d$ >1 时,5kHz-10kHz 频段的滤波系数基本不变,结合  $R_d$ 的选取原则确定  $R_d$ 的值。

[0094] 所述的网侧并联电阻  $R_g$ 不但能承担担电阻  $R_d$ 的部分作用,还有利于减少系统的总损耗,同时还能抑制两条并联的开关谐波支路的并联谐振点。 $R_g$ 与两条并联的开关谐波支路的并联阻抗  $Z_{//R}$ 为:

[0095]

$$Z_{//R} = \frac{R_g Z_{fz}}{R_g Z_{fm} + Z_{fz}}$$

[0096] 其中,

$$[0097] \qquad Z_{\rm fz} = S^4 L_{\rm f} C_{\rm f} L_{\rm fd} C_{\rm fd} + S^2 \left( L_{\rm f} C_{\rm f} + L_{\rm fd} C_{\rm fd} \right) + 1$$

[0098]  $Z_{fm} = S^3 C_f C_{fd} (L_f + L_{fd}) + S (C_f + C_{fd})$

[0099] 根据所述的  $Z_{//R}$  表达式绘制出分母模值  $|R_g Z_{fm} + Z_{fz}|$  与频率 f 和  $R_g$ 的关系图(附图 5),  $R_g$ 的选取应遵循: $Z_{//R}$ 的分母模值在并联谐振频率处取最小值,结合这个原则并参考附图 5 中的沟壑带选取  $R_g$ 的数值,从附图 5 中可以看到对应不同的并联谐振频率,都有一组  $R_g$ 值满足沟壑带。

[0100] 输出滤波电路,其特征在于,其转移导纳传递函数为:

[0101]

$$G_{\text{DRLCL}}(s) = \frac{i_{grid}(s)}{u_{invertor}(s)} = \frac{\alpha s^6 + \beta s^5 + \varepsilon s^4 + \delta s^3 + \eta s^2 + \mu s + \sigma}{\gamma_1 s^8 + \lambda_1 s^7 + \alpha_1 s^6 + \beta_1 s^5 + \varepsilon_1 s^4 + \delta_1 s^3 + \eta_1 s^2 + \mu_1 s}$$

[0102] 其中,

[0103]  $\gamma_1 = R_g L_1 L_2 R_d C_d C_h L_f C_f L_{fd} C_{fd}$

[0104]  $\lambda_1 = R_g L_1 L_2 L_f C_f L_{fd} (C_d + C_b) + L_1 L_2 R_d C_d L_f C_f L_{fd} C_{fd}$

[0105]  $\alpha_1 = L_f C_f L_{fd} C_{fd} (L_1 L_2 + R_g R_d C_d (L_1 + L_2)) + R_d C_d L_{fd} C_{fd} (C_b + C_f))$

[0106]  $+R_{g}L_{1}L_{2}(R_{d}C_{d}L_{f}C_{f}(C_{b}+C_{fd})$

[0107]  $\beta_1 = L_1 L_2 R_d C_d (L_{fd} C_{fd} + L_f C_f) + R_g (L_1 + L_2) L_f C_f L_{fd} C_{fd}$

[0108]  $+R_{g}L_{1}L_{2}(C_{fd}L_{f}C_{f}+L_{f}C_{f}(C_{h}+C_{d})+L_{fd}C_{fd}(C_{h}+C_{f}+C_{d}))$

[0109]  $\epsilon_1 = R_g R_d C_d (L_1 + L_2) (L_f C_f + L_{fd} C_{fd}) + L_1 L_2 (L_f C_f + L_{fd} C_{fd})$

[0110]  $+R_{g}R_{d}C_{d}L_{1}L_{2}(C_{h}+C_{f}+C_{f1})$

[0111]  $\delta_1 = R_g (L_1 + L_2) (L_f C_f + L_{fd} C_{fd})$

[0112]  $+R_aL_1L_2(C_d+C_h+C_f+C_{f1})+R_dC_dL_1L_2$

[0113]  $\eta_1 = R_{\sigma}R_{d}C_{d}(L_1 + L_2) + L_1L_2 \mu_1 = R_{\sigma}(L_1 + L_2)$

[0114]  $\alpha = L_2 R_s C_d L_f C_f L_{fd} C_{fd}$

[0115]  $\beta = R_g R_d C_d L_f C_f L_{fd} C_{fd} + L_2 L_f C_f L_{fd} C_{fd}$

[0116]  $\varepsilon = R_{\rho}L_{f}C_{f}L_{fd}C_{fd} + L_{2}R_{d}C_{d}(L_{fd}C_{fd} + L_{f}C_{f})$

[0117]  $\delta = (R_g R_d C_d + L_2) (L_f C_f + L_{fd} C_{fd})$

[0118]  $\eta = L_2 R_d C_d + R_g (L_f C_f + L_{fd} C_{fd})$

[0119]  $\mu = R_g R_d C_d + L_2 \sigma = R_g$

[0120] 其滤波系数为逆变侧流经电感 L1 的电流与网侧剩余电流之比的模,即前述的 Kw。

[0121] 有益效果:

[0122] 本发明的有源电力滤波器的输出滤波电路、滤波方法及设计方法,有源电力滤波器的输出滤波电路由逆变器侧电感  $L_1$ 、网侧电感  $L_2$ 、网侧并联电阻  $R_g$ 、阻尼支路  $R_d$ C<sub>d</sub>、高通支路  $C_h$ 、单倍开关谐波支路  $C_f$ L<sub>f</sub>、双倍开关谐波支路  $C_f$ L<sub>f</sub>。本发明的 DRLCL 电路可以有效的滤除 1kHz 以上的高次谐波,单倍及双倍开关谐波,滤波效果完全满足 1EEE519-1992 关于各次谐波的要求,并且不会增加控制系统的复杂性。

[0123] 本发明在传统的 LCL 输出滤波电路的基础上增加了 RC 阻尼支路和两条 LC 谐振支路,同时在网侧小电感上并联电阻,不但继承了 LCL 输出滤波电路的优点,同时还可以抑制了系统不稳定因素,有效的抑制高频谐波和开关纹波,滤波效果极佳,应用范围广(适用于单相或者三相有源电力滤波器),其设计方法亦可以作为并网逆变器的输出滤波电路设计的参考依据。

#### 附图说明

[0124] 图 1 是所述的 DRLCL 输出滤波电路单相电路图;

[0125] 图 2 是单 RC 阻尼支路与 RC+2 条开关谐波支路阻抗对比图;

[0126] 图 3 是  $R_d$ =0 时,  $K_w$ 和 k, f 的三维关系图;

[0127] 图 4 是 k=0.37 时, $K_w$ 和  $R_d$ ,f 的三维关系图;

[0128] 图 5 是分母模值  $|R_{g}Z_{fm}+Z_{fg}|$  与频率 f 和  $R_{g}$ 的关系图;

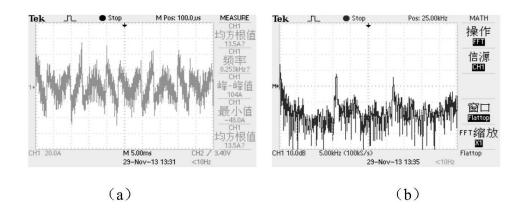

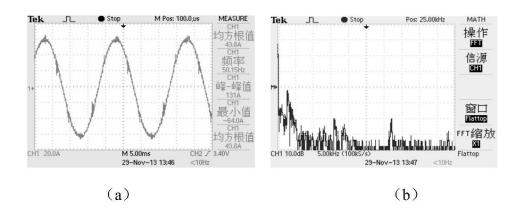

[0129] 图 6 是逆变器侧电感 L<sub>1</sub>上的电流波形 (a 图)及其 FFT 分析 (b 图);

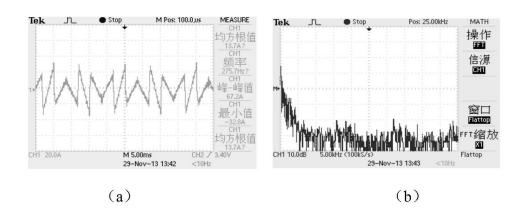

[0130] 图 7 是经过 DRLCL 滤波后有源电力滤波器输出电流波形 (a 图)及其 FFT 分析 (b

图);

[0131] 图 8 投入有源电力滤波器后电网电流波形 (a 图)及其 FFT 分析 (b 图)。

## 具体实施方式

[0132] 以下将结合附图和具体实施例对本发明做进一步详细说明:

[0133] 实施例 1:

[0134] 以下结合附图作详述,但不作为本发明的限定。

[0135] 一种有源电力滤波器(有源电力滤波器)的新型输出滤波电路(DRLCL)结构:

[0136] 所述的 DRLCL 电路,其特征在于,由逆变器侧电感  $L_1$ 、网侧电感  $L_2$ 、网侧并联电阻  $R_g$ 、阻尼支路  $R_d$ C<sub>d</sub>、高通支路  $C_h$ 、单倍开关谐波支路  $C_f$ L<sub>f</sub>、双倍开关谐波支路  $C_f$ L<sub>fd</sub>构成;

[0137] 其中,逆变侧电感  $L_1$ 接在逆变器侧 C 点和并联支路公共点 B 之间;网侧电感  $L_1$ 接 在网侧 A 点和并联支路公共点 B 之间;网侧并联电阻  $R_g$ 并联在网侧电感  $L_2$ 两端;阻尼支路中  $R_d$ 与  $C_d$ 串联后接在并联支路公共点 B 和 D 之间;高通支路  $C_h$ 接在并联支路公共点 B 和 D 之间;单倍开关谐波支路中  $C_f$ 与  $L_f$ 串联后接在并联支路公共点 B 和 D 之间;双倍开关谐波支路中  $C_f$ d与  $L_f$ d串联后接在并联支路公共点 B 和 D 之间;其中阻尼支路  $R_d$ Cd、高通支路  $C_h$ 、单倍开关谐波支路  $C_f$ Lf、双倍开关谐波支路  $C_f$ D、单倍开关谐波支路  $C_f$ D、单倍开关谐波支路  $C_f$ D、单位,其中阻尼支路  $C_f$ D、中枢,其中阻尼支路  $C_f$ D、中枢,其中枢  $C_f$ D、中枢  $C_$

[0138] 本发明所述的电路如附图 1 所示。图中逆变器侧电感  $L_1$ 用于平滑电压纹波;网侧电感  $L_2$ 用于抑制高频谐波;阻尼支路  $R_d$ C<sub>d</sub>用来抑制 LCL 电路结构的并联谐振尖峰,本电路谐振频率设计在 6kHz;两条 LC 开关谐振支路分别在  $f_s$ (单倍开关频率)和  $2f_s$ 处谐振,即在这两处频率为零阻抗;由于阻尼电阻  $R_d$ 的存在,高频衰减速度会减小,所以通过单电容支路  $C_h$ 是改善高频衰减特性;由于有两个并联开关谐振支路,所以会在  $f_s$ 和  $2f_s$ 之间引入一个并联谐振点,即本发明所述的  $f_{sp}$ ,会导致系统不稳定,用网侧并联  $R_g$ 来抑制这个并联谐振影响。

[0139] 所述的输出滤波电路的转移导纳传递函数为:

[0140]

$$G_{DRLCL}(s) = \frac{i_{grid}(s)}{u_{invertor}(s)} = \frac{\alpha s^6 + \beta s^5 + \varepsilon s^4 + \delta s^3 + \eta s^2 + \mu s + \sigma}{\gamma_1 s^8 + \lambda_1 s^7 + \alpha_1 s^6 + \beta_1 s^5 + \varepsilon_1 s^4 + \delta_1 s^3 + \eta_1 s^2 + \mu_1 s}$$

(1)

[0141] 其中,

[0142]  $\gamma_1 = R_g L_1 L_2 R_d C_d C_b L_f C_f L_{fd} C_{fd}$

```

\begin{tabular}{ll} \be

```

[0144]

$$\alpha_1 = L_f C_f L_{fd} C_{fd} (L_1 L_2 + R_g R_d C_d (L_1 + L_2)) + R_d C_d L_{fd} C_{fd} (C_b + C_f)$$

[0145]

$$+R_{g}L_{1}L_{2}(R_{g}C_{d}L_{f}C_{f}(C_{h}+C_{fd})$$

[0146]

$$\beta_1 = L_1 L_2 R_d C_d (L_{fd} C_{fd} + L_f C_f) + R_g (L_1 + L_2) L_f C_f L_f dC_{fd}$$

[0147]

$$+R_{\sigma}L_{1}L_{2}\left(C_{fd}L_{f}C_{f}+L_{f}C_{f}\left(C_{h}+C_{d}\right)+L_{fd}C_{fd}\left(C_{h}+C_{f}+C_{d}\right)\right)$$

[0148]

$$\epsilon_1 = R_a R_d C_d (L_1 + L_2) (L_f C_f + L_{fd} C_{fd}) + L_1 L_2 (L_f C_f + L_{fd} C_{fd})$$

[0149]

$$+R_{g}R_{d}C_{d}L_{1}L_{2}(C_{h}+C_{f}+C_{f1})$$

[0150]

$$\delta_1 = R_g (L_1 + L_2) (L_f C_f + L_{fd} C_{fd})$$

[0151]

$$+R_{\sigma}L_{1}L_{2}(C_{d}+C_{b}+C_{f}+C_{f1})+R_{d}C_{d}L_{1}l_{2}$$

[0152]

$$\eta_1 = R_g R_d C_d (1_1 + 1_2) + 1_1 1_2 \mu_1 = R_g (1_1 + 1_2)$$

[0153]

$$\alpha = L_2 R_d C_d L_f C_f L_{fd} C_{fd}$$

$$[0154] \qquad \beta = R_G R_d C_d L_f C_f L_{fd} C_{fd} + L_2 L_f C_f L_{fd} C_{fd}$$

[0155]

$$\epsilon = R_g L_f C_f L_{fd} C_{fd} + L_2 R_d C_d (L_{fd} C_{fd} + L_f C_f)$$

[0156]

$$\delta = (R_{\sigma}R_{d}C_{d} + L_{2}) L_{f}C_{f} + L_{fd}C_{fd}$$

[0157]

$$\eta = L_2 R_d C_d + R_g (L_f C_f + L_{fd} C_{fd})$$

[0158]

$$\mu = R_g R_d C_d + L_2 \sigma = R_g$$

[0159] 所述的 DRLCL 电路设计方法为:

[0160] DRLCL 电路设计顺序上先要设计逆变器侧电感  $L_1$ 的取值,然后确定网侧电感  $L_2$ 的值,进而根据相对应的 LCL 滤波要求设计总电容取值,最后讨论并联支路每个参数的设计方法。

[0161] 逆变器侧电感  $L_1$ 与网侧电感  $L_2$ 与并联电容总和  $C_{all}$ 选取原则与普通的 LCL 参数设计一样。

[0162] (1) 逆变器侧电感 L<sub>1</sub>的设计:

[0163]  $L_1$ 上同时流过了装置输出的低频谐波电流和开关纹波电流,所以  $L_1$ 的设计既要满足电流跟踪能力的要求,又要满足满足开关纹波电流的要求。即要满足表达式 (2),

[0164]

$$\frac{U_{dc}T_{s}}{8\times10\%I_{refm}} < L_{1} < \frac{5U_{dc}T_{s}}{3\Delta i_{ref}}$$

(2)

[0165] 其中, $I_{refm}$ 是有源电力滤波器输出峰值电流, $U_{dc}$ 是直流电压(700V),Ts 是开关周期(1 / 16000s), $\triangle$   $i_{ref}$ 为一个控制周期参考电流变化量,可以取为有源电力滤波器输出电流的 1 / 5。

[0166] (2) 所述的网侧电感 L<sub>2</sub>与并联电容总和 C<sub>all</sub>设计:

[0167] DRLCL 的电容设计要参考基本 LCL 参数设计,网侧电感  $L_2$ 和并联的总电容是抑制并网输出电流高频纹波,对低频段影响很小,所以两个参数的设计要综合考虑。电感  $L_1+L_2$  上的总压降不能高于 10%,同时为了保证有源电力滤波器的低频控制性能和高频滤波性能,LCL 输出滤波电路的谐振频率  $f_{res}$ 一股设计为  $:10f_1 < f_{res} < 0.5f_s$ , $f_1$ 是基波频率, $f_s$ 是单倍开关频率。并联电容的总数值要满足装置的无功功率的要求 : 并联支路总电容的无功容量要求小于装置无功容量的 5%。

[0168] 谐振频率表达式为:

[0169]

$$f_{res} = \frac{1}{2\pi} \sqrt{\frac{L_1 + L_2}{L_1 L_2 C_{all}}}$$

(3)

[0170] (3) 所述的并联支路其余参数设计:

[0171] 所述的 DRLCL 电路中 R<sub>g</sub>的主要作用是抑制两条谐振支路并联谐振峰值的作用,对于所需要的滤波频段的滤波性能几乎没有影响,所以对并联支路参数的影响可以忽略,讨论并联支路参数设计时,R<sub>g</sub>阻抗不计入在内。

[0172] 所述的单倍开关谐波支路和双倍开关谐波支路的阻抗包括一个并联谐振点和两个串联谐振点,对应的频率解分别为:

$$f_{s} = \frac{1}{2\pi\sqrt{L_{f}C_{f}}}, 2f_{s} = \frac{1}{2\pi\sqrt{L_{fd}C_{fd}}}$$

[0173]

$$f_{sp} = \frac{1}{2\pi}\sqrt{\frac{C_{f} + C_{fd}}{C_{f}C_{fd}(L_{fd} + L_{f})}}$$

(4)

[0174] 为保证两个谐振支路的滤波 Q 值相等,上述解还应满足:

[0175]

$$2f_s - f_{sp} = f_{sp} - f_s = \frac{1}{2}f_s$$

(5)

[0176] 由附图 2 可以看出,当  $C_h+C_f+C_{fd}=C'$ ,所述的并联支路中的去除高通支路  $C_h$ 的其他部分在低频段与 C' 和电阻 R' 构成的单一串联阻尼支路阻抗特性一致,区别仅在两个开关谐振点。所以所述的并联支路可以简化为 R' C' 阻尼支路和高通支路  $C_h$  并联。为均衡阻尼损耗和高频衰减效果, $C_h$ 设计与 C' 相等,即满足:

$$\begin{cases} C_h + C_f + C_{fd} = C_d = \frac{1}{2}C_{all} \\ C_h = \frac{1-k}{2}C_{all} \\ C_f = \frac{20k}{54}C_{all}, C_{fd} = \frac{7k}{54}C_{all} \end{cases} \tag{6}$$

[0178] 其中 0<k<1。

[0179] 由于电网电压不产生谐波,所以就谐波而言,电网侧相当于短路,所述的 DRLCL 滤波系数为 K<sub>M</sub>为逆变侧流经电感 L<sub>1</sub>的电流与网侧剩余电流之比的模:

[0180]

$$K_{M} = \left| \frac{i_{grid}(s)}{i_{invertor}(s)} \right| = \left| \frac{x + yj}{x_{1} + y_{1}j} \right|$$

(7)

[0181] 其中,

$$\begin{cases} x = \left(\frac{\omega^2}{\omega_{s1}^2} - 1\right) \left(\frac{\omega^2}{\omega_{s2}^2} - 1\right) \\ y = \frac{\omega R_d C_{all}}{2} \left(\frac{\omega^2}{\omega_{s1}^2} - 1\right) \left(\frac{\omega^2}{\omega_{s2}^2} - 1\right) \\ x_1 = 1 - \omega^2 (L_2 C_{all} + \frac{1}{\omega_{s1}^2} + \frac{1}{\omega_{s2}^2}) + \omega^4 \left[\frac{L_2 C_{all}}{\omega_{s1}^2} (1 - \frac{20}{54}k) + \frac{L_2 C_{all}}{\omega_{s2}^2} (1 - \frac{7}{54}k) + \frac{1}{\omega_{s1}^2 \omega_{s2}^2} \right] \\ - \omega^6 \frac{(2 - k) L_2 C_{all}}{2 \omega_{s1}^2 \omega_{s2}^2} \\ y_1 = \frac{\omega R_d C_{all}}{2} - \omega^3 R_d \left[\frac{L_2 C_{all}^2}{4} + \frac{C_{all}}{2} \left(\frac{1}{\omega_{s1}^2} + \frac{1}{\omega_{s2}^2}\right)\right] \\ + \omega^5 R_d \left[\frac{L_2 C_{all}^2}{4 \omega_{s1}^2} (1 - \frac{20}{27}k) + \frac{L_2 C_{all}^2}{4 \omega_{s2}^2} (1 - \frac{7}{27}k) + \frac{C_{all}}{2 \omega_{s1}^2 \omega_{s2}^2}\right] - \omega^7 \frac{L_2 R_d (1 - k) C_{all}^2}{4 \omega_{s1}^2 \omega_{s2}^2} \end{cases}$$

[0184]  $\omega$  是系统的各次谐波的角频率, $\omega_{s1}$ 是单倍开关谐波角频率, $\omega_{s2}$ 是双倍开关谐波角频率, $C_{a11}$ 是所述并联支路的所有电容的代数和。当  $R_d$ =0 时,通过绘制出  $K_M$ 和 k,f 的三维关系图(附图 3),k 的最优值应满足滤波系数对应系统谐振频率取最小值,参照附图 3: 当频率取得系统的谐振频率时,寻找 KM 的最小值即可确定最优 k=0. 37。

[0185] 选取最佳 k 值以后,通过绘制  $K_M$ 和  $R_d$ ,f 的的关系确定  $R_d$ , $R_d$ 的选取原则:应考虑阻尼损耗和高频谐波的滤波效果,一定范围内,其数值增大,滤波效果会变好,但是损耗会增加,数值减小,滤波效果会变差。参照附图 4,: $R_d$ >1 时,5kHz-10kHz 频段的滤波系数基本不变,结合  $R_d$ 的选取原则确定  $R_d$ 的值,本实施例取为  $2\Omega$ 。

[0186] (4) 网侧并联电阻 R。的设计

[0187] 所述的网侧并联电阻  $R_g$ 并联在网侧电感  $L_2$ 两侧,由于网侧电压并不产生谐波,所以对于谐波而言网侧相当于短路,即电阻与两条两条并联的开关谐波支路相当于,主要用与抑制两条并联的开关谐波支路的并联谐振点,同时配合  $R_a$ 抑制整个 DRLCL 电路系统的谐振点,由于网侧电感  $L_2$ 的内阻非常小,所有的输出电流几乎从网侧电感  $L_2$ 上流过,而  $R_g$ 上几乎没有电流,所以  $R_g$ 损耗非常小,这样电阻  $R_g$ 不但能承担担电阻  $R_d$ 的部分作用,还有利于减少系统的总损耗,同时还能抑制两条并联的开关谐波支路的并联谐振点。  $R_g$ 与两条并联的开关谐波支路的并联阻抗  $Z_{N_B}$ 为:

[0188]

$$Z_{//R} = \frac{R_g Z_{fz}}{R_g Z_{fm} + Z_{fz}}$$

(8)

[0189] 其中,

[0190]  $Z_{fz} = S^4 L_f C_f L_{fd} C_{fd} + S^2 (L_f C_f + L_{fd} C_{fd}) + 1$

[0191]  $Z_{fm} = s^3 C_f C_{fd} (L_f + L_{fd}) + a (C_f + C_{fd})$

[0192] 根据所述的  $Z_{//R}$  表达式绘制出分母模值  $|R_g Z_{fm} + Z_{fz}|$  与频率 f 和  $R_g$ 的关系图(附

图 5), $R_g$ 的选取应遵循: $Z_{//R}$ 的分母模值在并联谐振频率处取最小值,结合这个原则并参考附图 5 中的沟壑带选取  $R_g$ 的数值,从附图 5 中可以看到对应不同的并联谐振频率,都有一组  $R_g$ 值满足沟壑带,本实施例取值为  $1\Omega$ 。

[0193] 结合所述的参数设计方法,设计理想的仿真参数如表 I 所示:

[0194] 表 I DRLCL 参数

[0195]

| 参数                | 数值       |

|-------------------|----------|

| $L_1$             | 500uH    |

| $L_2$             | 30uH     |

| $R_{\rm g}$       | 1 Ω      |

| $R_{d}$           | 2 Ω      |

| C <sub>h</sub>    | 7.875uF  |

| $C_d$             | 12. 5uF  |

| $C_{\mathrm{f}}$  | 3. 426uF |

| $C_{\mathrm{fd}}$ | 1. 199uF |

| $L_{\rm f}$       | 28.881uH |

[0196]

| $L_{\rm fd}$ | 20. 631uH |

|--------------|-----------|

[0197] 由于工程制作工艺的限制,对表 I 的个别参数做近似处理:

[0198]  $C_h$ =8uF,  $C_f$ =3. 5uF,  $C_f$ d=1. 2uF,  $L_f$ = 29uH,  $L_f$ d=20uH, 其他参数与表 I 中一致。上述参数应用于在 66KVA 的三相三线有源电力滤波器的样机,得到滤波前后波形图及 FFT 分析图,如附图 6-8 所示。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8